· 工程实践

# 成膜基板烧结异常的分析及改进

# 王尚智 赵 丹

(山东航天电子技术研究所,烟台 264000)

文 摘 某成膜基板在烧结后出现了析出透明物质的异常现象,严重影响了基板的键合强度。通过外观检查、SEM 分析和能谱分析等手段,确定析出物为导体浆料中的玻璃相。分析结果表明,印刷厚度较厚是造成本次基板烧结异常的主要原因,但降低印刷厚度会对产品电性能产生影响。

关键词 成膜基板,烧结,玻璃,SEM

中图分类号:TG146.3+9

DOI:10.3969/j. issn. 1007-2330. 2014. 04. 022

# Analysis and Improvement of Film Substrate Anomaly Sintering

WANG Shangzhi ZHAO Dan

(Shandong Aerospace Electro-Technology Institute, Yantai 264670)

**Abstract** A film substrate appear abnormal phenomenon of transparent material precipitation in the sintering process, seriously affecting the strength of bonding. Through visual inspection, SEM analysis and spectrum analysis, the main components of transparent material precipitated was determined as glass. After analysis, the thickness of the printing exceeded is the main reason for the abnormal substrate sintering, However, decrease the thickness of the printing will affect product performance.

**Key words** Substrate, Sintering, Glass, SEM

#### 0 引言

成膜基板指通过丝网印刷的方式,将各种导体浆料、电阻浆料及介质浆料等依次印制到陶瓷基板上,再通过烘干和烧结形成所需要的电路图形。作为混合集成电路中厚膜元件、裸芯片及其他片式元器件的主要支撑体,其重要性不言而喻。

某型号产品成膜基板在烧结过程中出现焊盘析出透明物质的异常现象,严重影响产品的键合强度。本文通过对该透明物质的形貌和主要成分进行分析,确定了其主要来源和产生机理,并根据分析结果,改进工艺,经试验验证,烧结后的基板满足产品要求。

#### 1 问题描述

某型号成膜基板在焊接层烧结完成后,发现焊盘 周围有透明状物质析出(图1),而印刷后、烘干后目 检时均未发现异常。多次重烧后,该透明物质依然存 在,并且有随着重烧次数的增多而不断扩散的趋势。

基板焊接层印制采用的是 Dupont 铂钯银浆料,

在焊接层印制之前,该基板已制作完成了背面导体层、正面导体层,使用的是同型号、同批次的浆料,烘干和烧结工艺也都相同,均未发现异常。

图 1 基板焊盘烧结异常示意图

Fig. 1 Abnormal of substrate pad sintering

#### 2 问题分析

借助外观检查、SEM 和 EDS 等手段,对析出物进行了细致的分析:

#### 2.1 外观检查

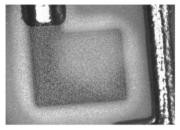

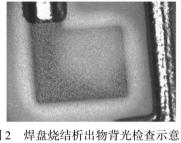

使用背光显微镜对基板异常部位进行了外观检

收稿日期: 2014-05-22

作者简介:王尚智,1985年出生,工程师,主要从事厚膜成膜基板制造研究。E-mail:let203@163.com

杳(图2),可以看到析出物沿着焊盘均匀分布,最大 外扩宽度达到了500 µm。

图 2 焊盘烧结析出物背光检查示意图

Fig. 2 Pad sintering precipitate backlight inspection

2.2 SEM 观察

说明填充物质的量是非常大的。

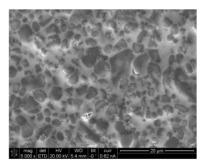

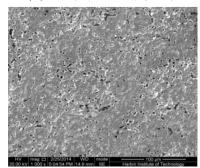

使用扫描电镜对焊盘、周边析出透明物质区域

(以下简称扩线区域)和陶瓷基板的表面形貌进行了 观察,结构差异非常明显。从图3可见,焊盘烧结后 表面功能相分布均匀有规律:周围陶瓷基板颗粒均 匀.无异常材质出现:而扩线区域陶瓷基板空隙被白 色物质完全填充,填充厚度几乎与陶瓷颗粒相平齐,

焊盘 (a)

陶瓷基板

扩线区域

焊盘、扩线区域和陶瓷基板的 SEM 图

SEM of pad, extended-line area and ceramic substrate

## 2.3 EDS 分析

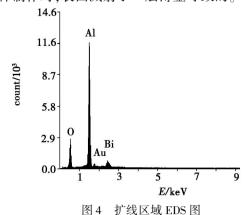

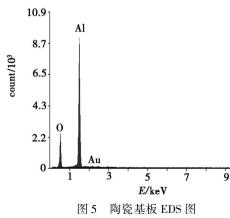

图 4 发现,焊盘周边扩线区域主要含有 Bi 元素, 没有发现 Ag、Pd、Pt 元素。对比陶瓷基板 EDS 图像 (图5)可知,其主要含有 Al、O、Au 元素,其中 Al、O 元素是其本身 Al,O, 材质决定的, Au 的存在是由于 试样制作时,表面溅射了一层薄金导致的。

Fig. 4 EDS of extended-line area

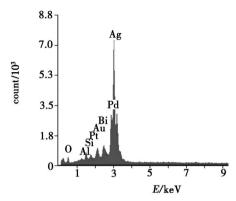

由图 6 可知,焊盘主要含有 Al、O、Ag、Pt、Pd、Bi、 Au、Si 等元素,其中 Al、O 元素来自于焊盘底部的陶 瓷基板, Ag、Pt、Pd、Bi、Si 元素是浆料中的固有成分, Au 源自于试样制作时溅射的薄金。

扩线区域经扫描主要含有 Al、O、Bi、Au 元素,其 中Al、O元素来自于底部的陶瓷基板,Au源自于试样 制作时溅射的薄金。

Fig. 5 EDS of substrate

图 6 焊盘 EDS 图

Fig. 6 EDS of pad

由于 Bi 是浆料玻璃相的重要组成元素,同时查 阅厂家提供的浆料 MSDS 表,得知浆料中含有大约 10%的 Bi 成分,因此推断出扩线区域的 Bi 元素来自

于铂钯银浆料中的固有成分,焊盘周边析出的透明物质为浆料中的玻璃相。

#### 3 问题定位

基板焊盘烧结后析出玻璃相,最主要的原因有三个:浆料异常、基板烘干、烧结过程异常以及基板焊接 层印刷异常。

### 3.1 浆料异常

经查,焊接层焊盘印制所使用的 Dupont 铂钯银 浆料在有效期范围内,入所检验评价合格,同时,正面 导体层与焊接层使用的是同一罐浆料,在同一天印制,未出现异常,因此该原因可以排除。

#### 3.2 烘干、烧结异常

基板正面导体层与焊接层为同一天烘干、烧结, 参数相同,正面导体层烧结后未出现异常。

在焊接层烧结异常后,立即对烘干炉和烧结炉的 炉温曲线进行了重新标定,均满足规范要求,因此该 原因可以排除。

#### 3.3 印刷异常

焊接层印刷后按《丝网印刷检验规范》的要求进 行了外观目检,未发现异常。

通常基板正面焊盘制作采用的是"印-烘-烧-印-烘-烧"的工艺方法,即在印烧一层导体层(正面导体层)后.再在上面加印一层(焊接层)。

成膜基板设计文件规定焊接层烧结后的厚度要达到 28~35 μm,为达到设计要求的膜层厚度,对正面导体层和焊接层的印刷厚度均进行了加厚,规定正面导体层烧结后膜层厚度应在 14~18 μm 内,焊接层烧结后膜层厚度应在 28~35 μm 内。

正面导体层厚度在标准要求的范围内,烧结后未出现异常,而焊接层烧结后的厚度远远超过现有成熟工艺的膜厚范围,因而出现了烧结后析出玻璃相的异常现象。

通过进行原因分析,排除了浆料和烘干、烧结导致异常现象发生的可能性,因此确定设计要求的印刷厚度超标是造成此次异常现象的主要原因。

#### 4 机理分析

正面导体层烧结完成后,表面功能相颗粒细小均匀,分布规律,周围含有相对均匀的孔隙(图7)。孔隙的形成是由于浆料内的有机载体在烧结过程中,不断挥发所致,属正常现象。

焊接层在烧结过程中,熔融的玻璃与正面导体层发生物理和化学反应<sup>[1]</sup>,形成层间导电相。化学反应主要是熔融的玻璃与下层导体中的导电颗粒产生浸润,将导电颗粒粘附形成导电相,物理反应主要是熔融的玻璃注入到下层导体表面的孔隙处,形成物理黏附。

当印刷的浆料层厚度较厚时,单位面积焊盘中含有的玻璃相较多,在烧结过程中,只有少量的玻璃相

进行了化学反应,而更多的则沿着焊盘表面的孔隙逐渐渗透,最终到达了陶瓷基板上,形成了析出透明状物质的异常现象。多次重烧过程中,熔融的玻璃持续渗透,因而扩线现象不断加剧。

a) 超景深光学显微镜观察

(b) 扫描电子显微镜观察 图 7 正面导体层焊盘烧结后表面形貌

Surface morphology of positive conductor layer

## 5 改进措施

减小单位面积焊盘的玻璃相含量是解决本次烧结异常的最直接方法主要有两个:一是降低焊盘的印刷厚度,二是换用低玻璃相含量的导体材料。

由于该型号成膜基板功率大,电流承载能力要求高,降低焊盘的膜厚将导致产品功率密度超标,影响长期稳定性,方法不可取。

经调研,选取了一款低玻璃相含量的导体浆料, 替代现有的铂钯银浆料,按以上工艺流程重新印制基 板正面电路图形,烧结后目检未出现异常现象。

将试制合格的成膜基板进行附着力、芯片剪切力等 多项检验评价试验,均顺利通过,各项指标满足要求。

#### 6 结语

成膜基板是混合集成电路的一个重要载体,由于 成膜基板制作过程较为复杂,影响因素很多,因此在 产品设计时,应加强对所用材料的分析、了解,尽量选 用通用、成熟的工艺技术,才能从根本上保证产品的 生产质量。

#### 参考文献

[1] Charles A. Harper. 电子封装与互连手册[M]. 电子工业出版社,2009;427

(编辑 任涛)